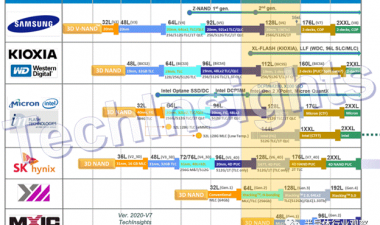

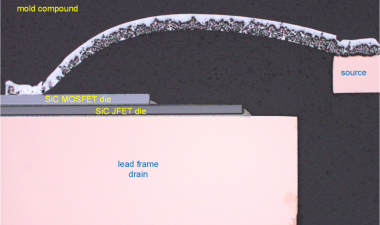

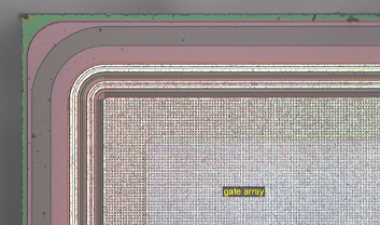

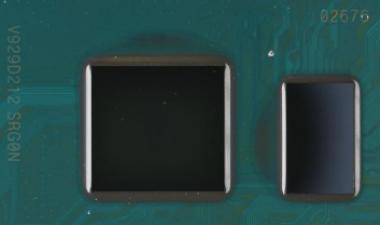

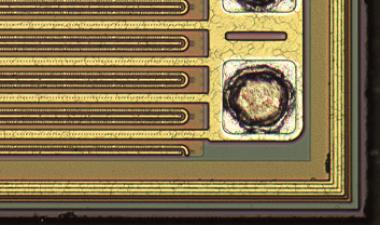

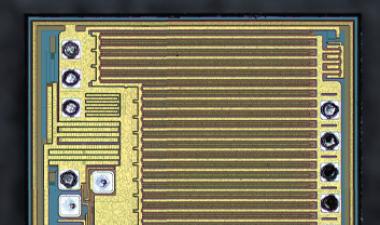

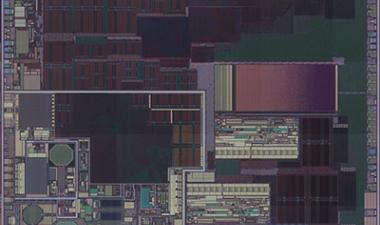

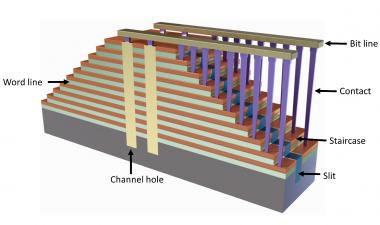

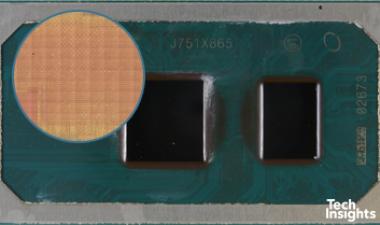

skhynix发布了世界上第一个128层(128L)3D NAND,他们称之为4D NAND。这是他们的第二代NAND使用外围下单元(PUC)架构构建;第一代是他们的96L NAND。

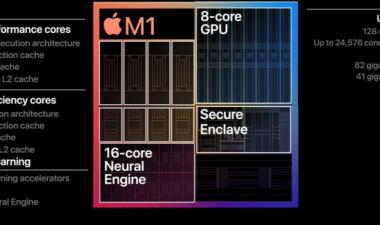

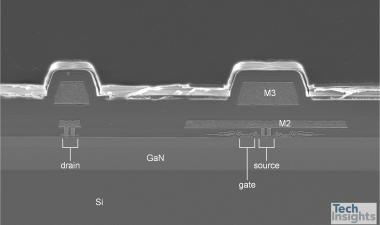

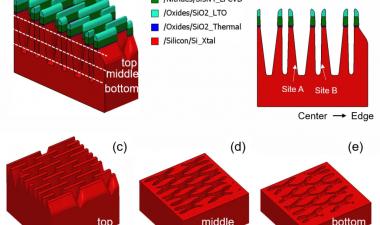

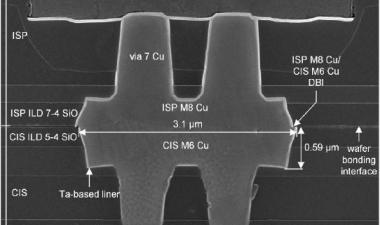

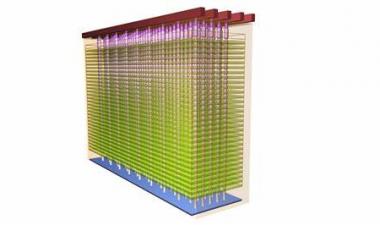

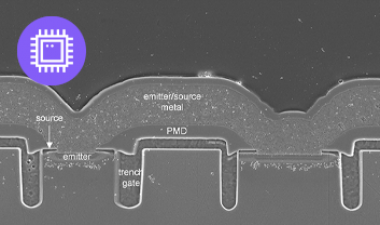

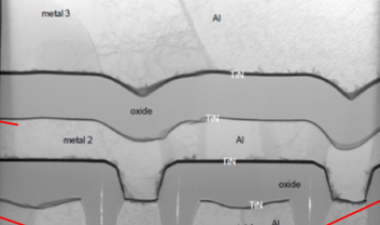

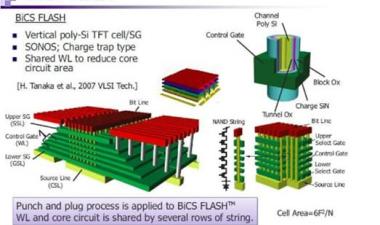

In PUC architecture, peripheral circuits are stacked under the cell, resulting in higher 3D NAND bit density, and improving performance and capacity. This approach is comparable to Micron & Intel’s CuA (CMOS circuitry under cell array) and YMTC’s Xtacking (where peripheral circuitry and NAND array are processed separately and then hybrid bonded).

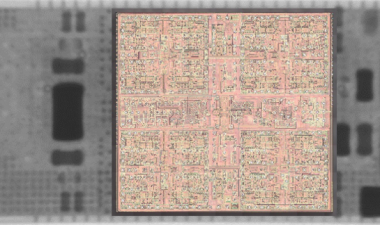

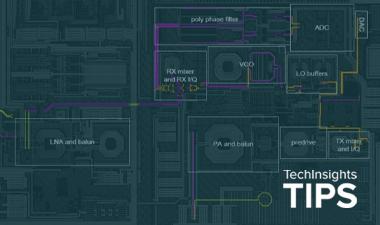

SK hynix 128L 3D PUC NAND(4D NAND)分析

下载TechInsights的SK hynix 128L PUC 3D NAND分析,包括市场概述、新技术概述、分析细节等。

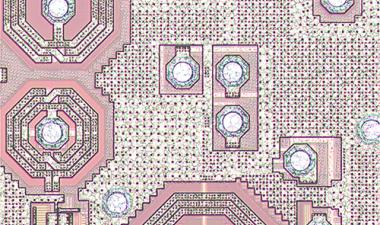

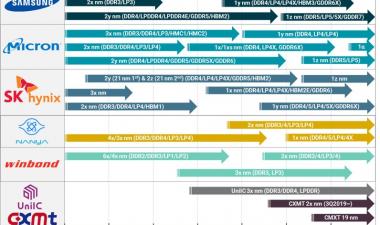

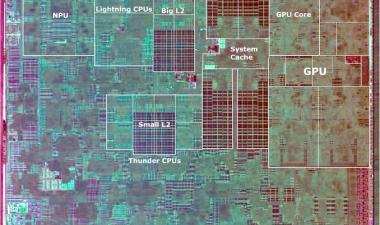

根据我们对这项新技术的早期分析,与之前的SK hynix 72L/76L P-BiCS和SK hynix 96L PUC相比,我们观察到以下几点:

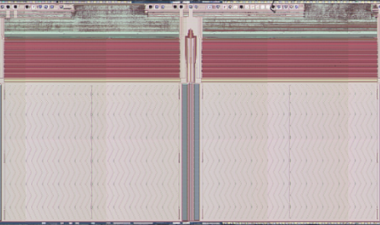

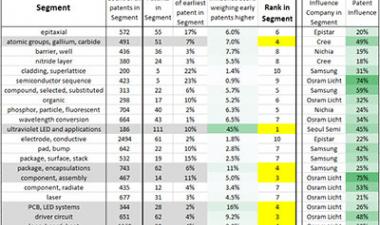

| SK海力士72L/76L P-BiCS | SK海力士96L PUC (4D和1)圣发电机) |

SK海力士128L PUC (4D和2)钕发电机) |

|

|---|---|---|---|

| 3D NAND版本。 | 第4版 | 版本5 | V6发动机 |

| #堆叠 | 2 | 2 | 2 |

| #累计门数 | 82/86 (不包括PCG) |

115 | 147 |

| #总活动WLs | 72/76 | 96 | 128 |

| #选择器 | 3个SGS+3个SGD | 7个SGS+3个SGD | 7个SGS+3个SGD |

| 垂直电池效率 (VCE)1 |

87.8 % / 88.4 % | 83.5% | 87.1% |

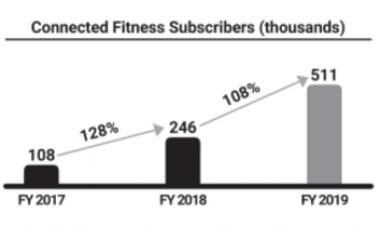

| 钻头密度 | 4.30 Gb/毫米2 | 6.30 Gb/毫米2 | 8.15 Gb/毫米2(expected) |

1VCE总门中#活动单元的百分比,(#活动WLs)/(#总门)x100%

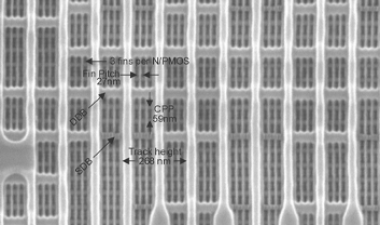

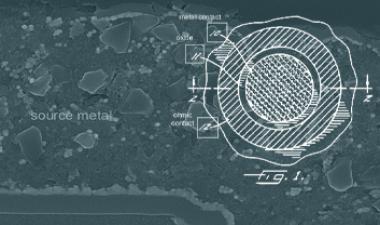

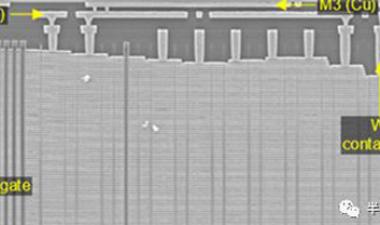

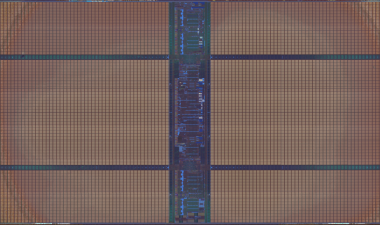

- The 1st gen. 4D NAND PUC 96L products (V5) showed 115 gates in total on a silicon source plate

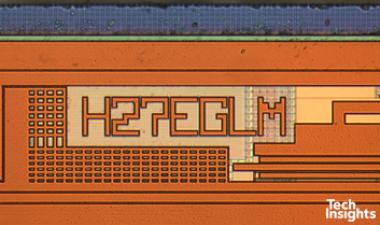

- 第二代PUC 128L产品(V6)总共使用147个门,可能包括9个虚拟字线(dwl)、7个选择门源端(SGS)和3个选择门漏端(SGD)

- 这意味着垂直单元效率提高到87.1%,TLC芯片上的内存位密度约为8.15GB/mm2

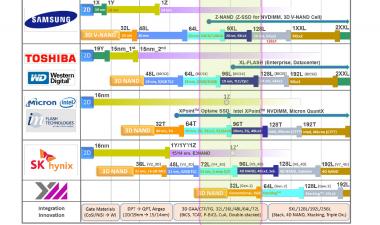

通过增加图层(即从76L增加到96L,现在又增加到128L)所提供的位密度的增加,正在推动技术边界,无疑将使竞争继续进行下去。位密度的增加也会影响其他NAND内存设计方面,这将变得更具挑战性,从头开始解决(即没有公正的第三方洞察)。

TechInsights预计,未来几个月,所有主要制造商都将推出约128L的产品。我们期待着分析和比较不同的解决办法。