由Sinjin Dixon-Warren博士贡献

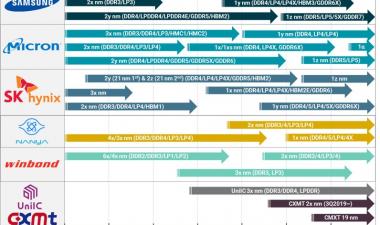

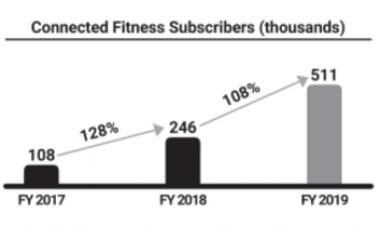

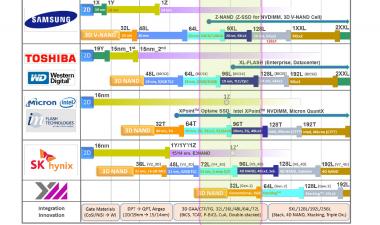

台积电的28纳米CMOS技术平台是目前最先进的产品。我们的分析表明,对于台积电及其无晶圆厂设计合作伙伴来说,这将是一个非常有利可图的技术平台。事实上,公司董事长张瑞敏预计,28纳米将成为有史以来最大的节点,产量将超过65纳米节点,高峰时每月将超过13万片晶圆。

从历史上看,台积电与FPGA供应商Altera或Xilinx等领先客户的合作速度较慢;采用28纳米技术的公司包括高通(Qualcomm)和其他移动驱动公司,需求的转变速度要快得多。因此,虽然在今年第一季度,28纳米技术仅占销售额的5%左右,但在最后一个季度,这一比例预计将超过20%。

在SEMATECH在纽约萨拉托加举行的第九届先进门堆栈技术国际研讨会上,台积电的Meikei Ieonge介绍了台积电的28纳米产品(一些细节可以在之前的博客文章中找到)。台积电的28纳米技术有四种版本,目前正在为包括Xilinx、Altera、AMD、高通等在内的多家制造商批量发货。

台积电成立于1987年,是全球最大的晶圆代工厂,2011年营收达145亿美元。根据他们的网站,2011年他们的总产能为1320万八英寸晶圆当量。他们目前提供从>0.5微米到28纳米的全系列CMOS技术。

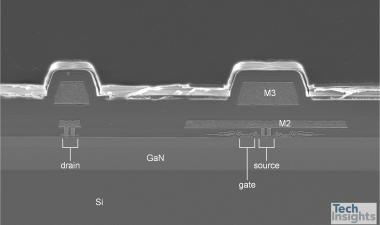

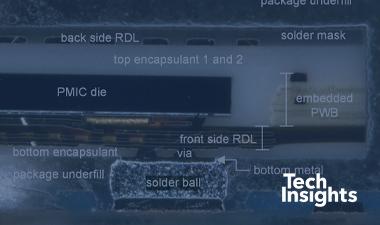

28纳米技术平台于2010年投入生产,并提供了四种工艺变体,分别为HP、HPM、HPL和LP。到目前为止,我们已经分析了其中的三种工艺变体,即HP、HPL和LP。28纳米一代是台积电首次使用高k金属栅极(HKMG)晶体管。HP和HPL技术采用HKMG晶体管,而LP使用传统的多聚栅极,带有ONO栅极电介质。台积电声称他们的28纳米工艺技术在2010年投入生产;然而,直到2011年年中,生产设备才可用于分析。

台积电最先进工艺技术的早期采用者仍包括两家领先的FPGA制造商Xilinx和Altera。这些公司生产高价值、相对低产量的器件,因此可以承担新CMOS技术早期阶段相对较低的产量。毫无疑问,第一个进入我们实验室的新技术节点的设备通常来自这些供应商;自2002年我们对130纳米Altera Stratix和2004年对90纳米Altera Stratix II进行分析以来,情况一直如此。当时,Altera Stratix的钴硅化聚晶体管的接触栅极间距为530nm,而Stratix II中的晶体管的接触栅极间距为370nm。

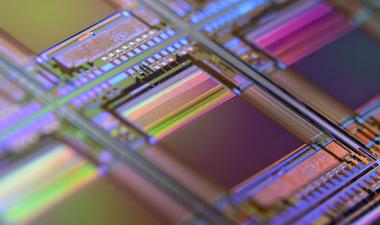

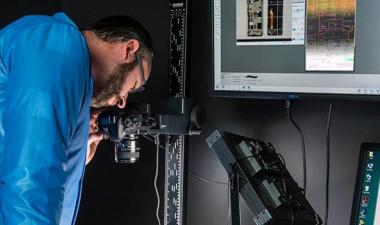

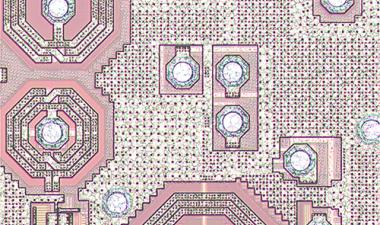

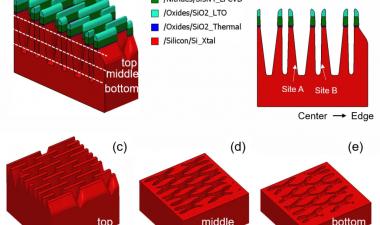

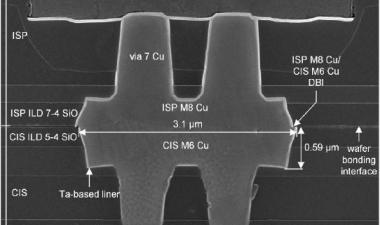

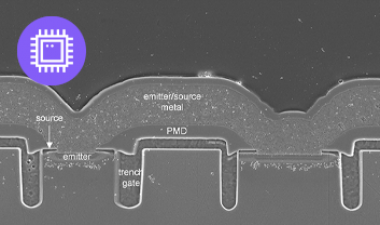

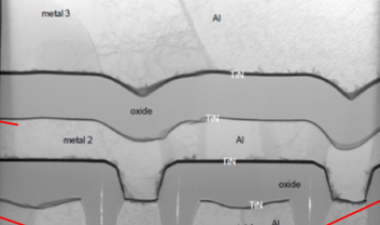

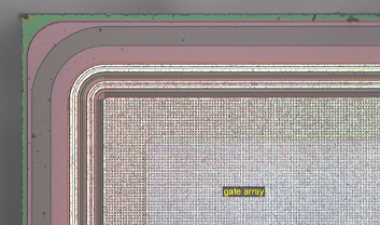

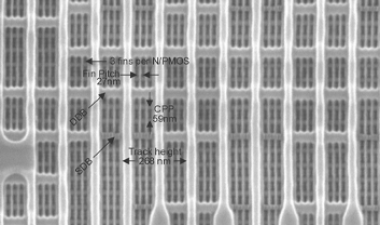

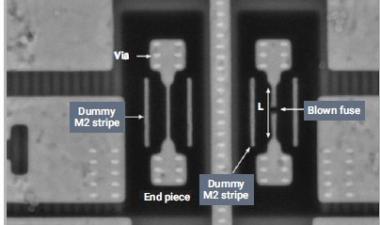

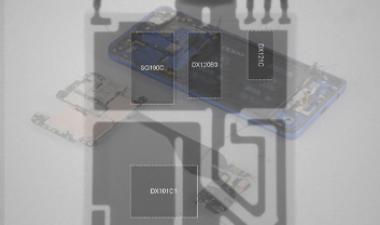

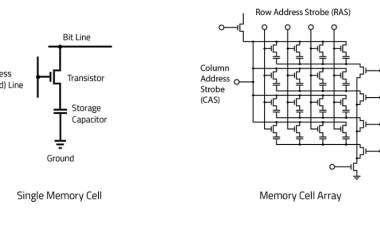

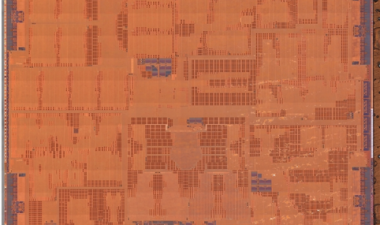

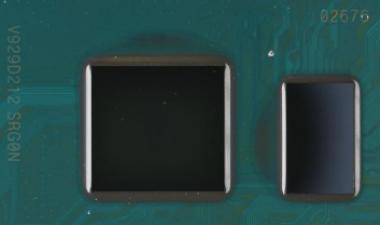

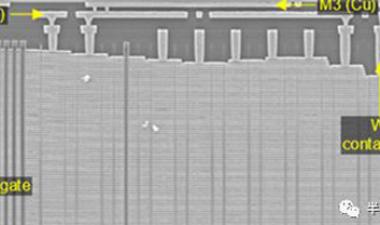

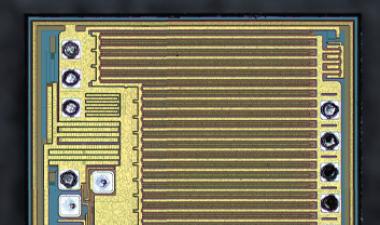

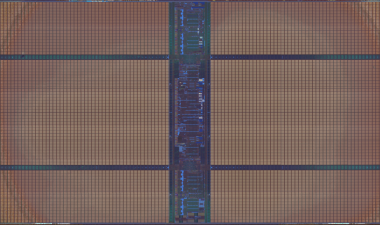

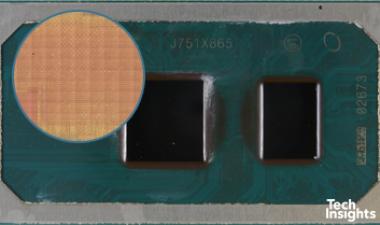

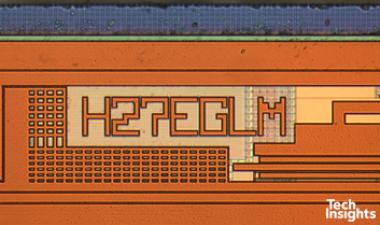

Xilinx XC7K325T Kintex-7是我们实验室看到的第一个28纳米台积电技术。我们在2011年7月发布了结构分析报告。XC7K325T采用台积电的HPL技术制造,并具有11层后端金属化。HKMG晶体管将通道方向旋转到PMOS晶体管的方向,以提高PMOS晶体管的性能。嵌入式SiGe未用于PMOS源/漏。晶体管的冶金工艺与英特尔32纳米技术非常相似,PMOS采用TiN金属栅极,NMOS采用TiAlN金属栅极。HK层采用氧化铪介质,覆盖2.0 nm厚的二氧化硅层。晶体管是由一个多晶硅栅极替换,“栅极最后”过程,类似于英特尔所使用的。基本上,聚晶体管已经形成,所有的源/漏工程已经完成。然后去除聚合物,代之以NMOS和PMOS金属化。 The contacted gate pitch for the transistors in the XC7K325T is 120 nm. According to TSMC the HPL process is optimised for high performance with low leakage.

Altera 5SGXEA7K2F40C2ES Stratix V是我们实验室分析的第二个28纳米台积电技术。我们的流程审查报告于2011年10月发布。Stratix V采用28 nm HP工艺制造,其特点是在PMOS晶体管的源/漏区嵌入SiGe,后端有12层金属。HKMG的结构与HPL工艺中使用的结构基本相同,但具有更薄的(1.2 nm) SiO2层,适合HP工艺。5SGXEA7K2F40C2ES晶体管的接触栅极间距为120 nm。根据台积电的说法,28纳米HP工艺的目标是更高的速度和性能,他们声称与40纳米工艺相比,速度提高了45%,每个栅极的泄漏量相同。

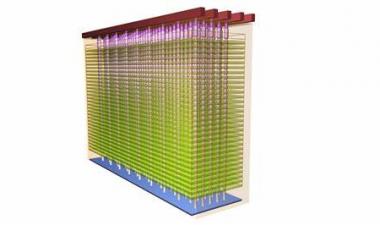

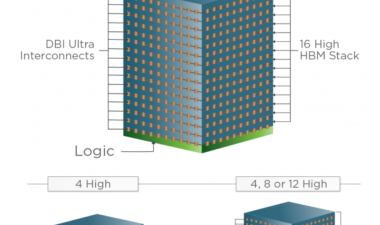

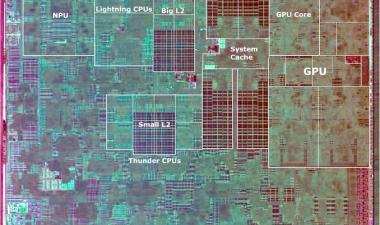

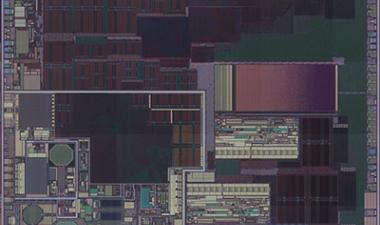

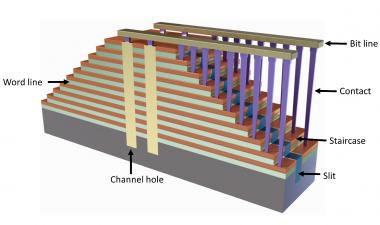

FPGA制造商并没有在他们的芯片设计中广泛使用高密度SRAM。在这里,我们将目光投向AMD的图形部门和nVidia,它们都是台积电新工艺技术的早期采用者。他们的图形处理芯片包含大量高密度的6T-SRAM。我们通常发现AMD/ATI或nVidia是第一批使用台积电先进技术的完整功能集的芯片,包括高密度SRAM。

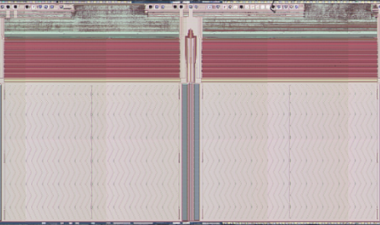

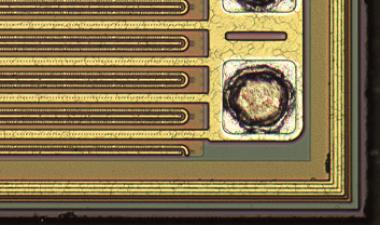

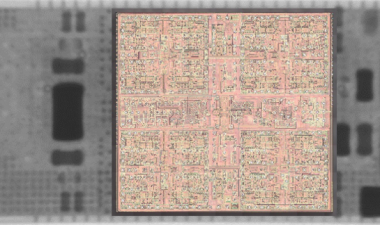

今年早些时候,我们完成了对AMD radiontm HD 7970 215-0821060图形处理器上高密度SRAM的有限分析,该处理器是用台积电的HP工艺制造的。我们的TEM分析证实了215-0821060晶体管结构与Altera Stratix V器件相同,因为两者都基于TSMC 28 nm HP工艺。215-0821060具有0.16 μ m26T-SRAM,晶体管以单轴布局排列。相比之下,从ATI Radeon X1950 Pro显卡中提取的90纳米ATI 215PADAKA12FG图形处理器的SRAM单元大了5倍多,为0.86µm2.

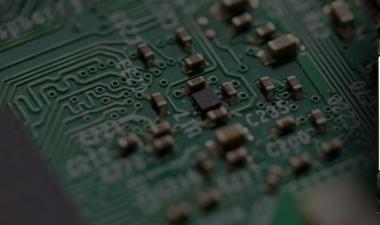

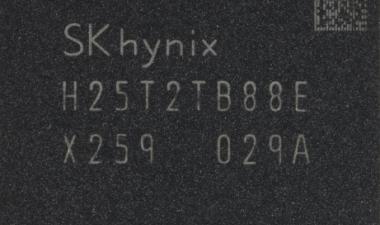

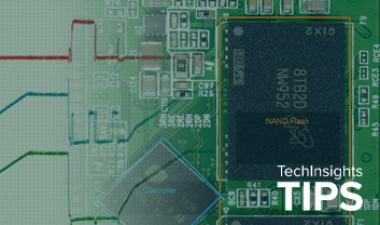

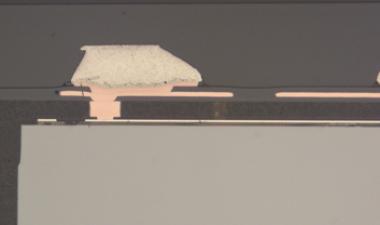

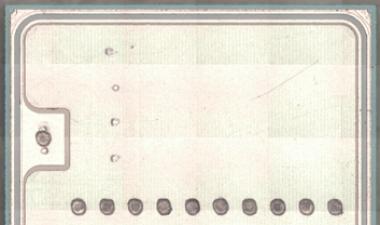

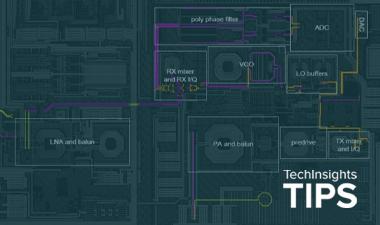

2012年早些时候,我们在高通MSM8960骁龙S4片上系统中发现了台积电28纳米LP工艺的一个例子。28 nm LP工艺采用多晶硅门,嵌入SiGe,用于提高PMOS性能。低功率(LP)工艺显然是第一个完成台积电所有资格测试的工艺。台积电声称,28纳米LP工艺是低成本和快速上市的选择,是低待机功率应用(如蜂窝基带)的理想选择。在每个栅极的泄漏量相同的情况下,该工艺明显比40 nm LP工艺提高了20%的速度。

最小接触栅距为120 nm。28纳米LP工艺本质上是台积电40纳米LP工艺的缩小版(增加了用于PMOS的e-SiGe),该工艺(值得注意的是)用于制造NVIDIA Tegra T20-H-A2应用处理器。40 nm LP工艺在逻辑区域具有160 nm的接触栅间距。

台积电提供的第四个也是最后一个28纳米工艺是HPM技术。该工艺针对移动应用,显然将在同一芯片上支持高性能晶体管和低功率晶体管,从而实现更高性能的移动设备,同时继续提高电源性能,这对电池供电的设备至关重要。台积电声称,该技术可以提供比28纳米HP更好的速度,同时提供与28纳米LP相似的泄漏功率。广泛的性能/泄漏覆盖显然使28纳米HPM成为从网络、平板电脑到移动消费产品的理想应用。HPM工艺还没有出现在市场上,但Chipworks预计很快就会在领先制造商的移动设备上看到这种技术的例子——可能是苹果A6的未来变种。